# **JVC** SERVICE MANUAL

# MICRO COMPONENT MD SYSTEM

# UX-A70MDR

### Contents

| Safety precautions            | 1-2  |

|-------------------------------|------|

| Preventing static electricity | 1-4  |

| Important for laser products  | 1-6  |

| Disassembly method            | 1-7  |

| Main adjustment               | 1-29 |

| Flow of functional operation  |      |

| until TOC read (CD)           | 1-33 |

| Flow of functional operation  |      |

| until TOC read (MD)           | 1-34 |

|                               |      |

Maintenance of laser pickup ------ 1-35 Replacement of laser pickup ------ 1-35 Maintenance of MD pickup ------ 1-36 Procedures of changing the MD pickup ------ 1-36 Description of major ICs ------ 1-37~57

### -Safety Precautions -

- 1. This design of this product contains special hardware and many circuits and components specially for safety purposes. For continued protection, no changes should be made to the original design unless authorized in writing by the manufacturer. Replacement parts must be identical to those used in the original circuits. Services should be performed by qualified personnel only.

- 2. Alterations of the design or circuitry of the product should not be made. Any design alterations of the product should not be made. Any design alterations or additions will void the manufacturer's warranty and will further relieve the manufacture of responsibility for personal injury or property damage resulting therefrom.

- 3. Many electrical and mechanical parts in the products have special safety-related characteristics. These characteristics are often not evident from visual inspection nor can the protection afforded by them necessarily be obtained by using replacement components rated for higher voltage, wattage, etc. Replacement parts which have these special safety characteristics are identified in the Parts List of Service Manual. Electrical components having such features are identified by shading on the schematics and by (⚠) on the Parts List in the Service Manual. The use of a substitute replacement which does not have the same safety characteristics as the recommended replacement parts shown in the Parts List of Service Manual may create shock, fire, or other hazards.

- 4. The leads in the products are routed and dressed with ties, clamps, tubings, barriers and the like to be separated from live parts, high temperature parts, moving parts and/or sharp edges for the prevention of electric shock and fire hazard. When service is required, the original lead routing and dress should be observed, and it should be confirmed that they have been returned to normal, after re-assembling.

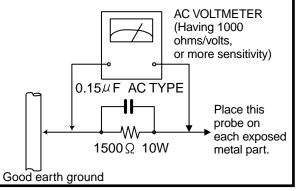

- 5. Leakage currnet check (Electrical shock hazard testing) After re-assembling the product, always perform an isolation check on the exposed metal parts of the product (antenna terminals, knobs, metal cabinet, screw heads, headphone jack, control shafts, etc.) to be sure the product is safe to operate without danger of electrical shock. Do not use a line isolation transformer during this check.

- Plug the AC line cord directly into the AC outlet. Using a "Leakage Current Tester", measure the leakage current from each exposed metal parts of the cabinet, particularly any exposed metal part having a return path to the chassis, to a known good earth ground. Any leakage current must not exceed 0.5mA AC (r.m.s.)

- Alternate check method

Plug the AC line cord directly into the AC outlet. Use an AC voltmeter having, 1,000 ohms per volt or more sensitivity in the following manner. Connect a 1,500 $\Omega$  10W resistor paralleled by

a  $0.15\mu$ F AC-type capacitor between an exposed metal part and a known good earth ground. Measure the AC voltage across the resistor with the AC voltmeter. Move the resistor connection to eachexposed metal

part, particularly any exposed metal part having a return path to the chassis, and meausre the AC voltage across the resistor. Now, reverse the plug in the AC outlet and repeat each measurement. voltage measured Any must not exceed 0.75 V AC (r.m.s.). This corresponds to 0.5 mA AC (r.m.s.).

### -Warning

- 1. This equipment has been designed and manufactured to meet international safety standards.

- 2. It is the legal responsibility of the repairer to ensure that these safety standards are maintained. 3. Repairs must be made in accordance with the relevant safety standards.

- 4. It is essential that safety critical components are replaced by approved parts.

- 5. If mains voltage selector is provided, check setting for local voltage.

A CAUTION Burrs formed during molding may be left over on some parts of the chassis. Therefore, pay attention to such burrs in the case of preforming repair of this system.

### Safety precautions (U.K only)

- 1. This design of this product contains special hardware and many circuits and components specially for safety purposes. For continued protection, no changes should be made to the original design unless authorized in writing by the manufacturer. Replacement parts must be identical to those used in the original circuits.

- 2. Any unauthorised design alterations or additions will void the manufacturer's guarantee ; furthermore the manufacturer cannot accept responsibility for personal injury or property damage resulting therefrom.

- 3. Essential safety critical components are identified by ( ⊥) on the Parts List and by shading on the schematics, and must never be replaced by parts other than those listed in the manual. Please note however that many electrical and mechanical parts in the product have special safety related characteristics. These characteristics are often not evident from visual inspection. Parts other than specified by the manufacturer may not have the same safety characteristics as the recommended replacement parts shown in the Parts List of the Service Manual and may create shock, fire, or other hazards.

- 4. The leads in the products are routed and dressed with ties, clamps, tubings, barriers and the like to be separated from live parts, high temperature parts, moving parts and/or sharp edges for the prevention of electric shock and fire hazard. When service is required, the original lead routing and dress should be observed, and it should be confirmed that they have been returned to normal, after re-assembling.

### Warning

- 1. Service should be performed by qualified personnel only.

- 2. This equipment has been designed and manufactured to meet international safety standards.

- 3. It is the legal responsibility of the repairer to ensure that these safety standards are maintained. 4. Repairs must be made in accordance with the relevant safety standards.

- 5. It is essential that safety critical components are replaced by approved parts.

- 6. If mains voltage selector is provided, check setting for local voltage.

A CAUTION Burrs formed during molding may be left over on some parts of the chassis. Therefore, pay attention to such burrs in the case of preforming repair of this system.

# **Preventing static electricity**

Electrostatic discharge (ESD), which occurs when static electricity stored in the body, fabric, etc. is discharged, can destroy the laser diode in the traverse unit (optical pickup). Take care to prevent this when performing repairs.

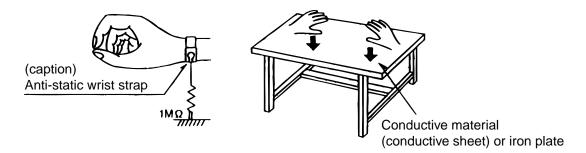

### 1.1. Grounding to prevent damage by static electricity

Static electricity in the work area can destroy the optical pickup (laser diode) in devices such as DVD players. Be careful to use proper grounding in the area where repairs are being performed.

### 1.1.1. Ground the workbench

1. Ground the workbench by laying conductive material (such as a conductive sheet) or an iron plate over it before placing the traverse unit (optical pickup) on it.

### 1.1.2. Ground yourself

1. Use an anti-static wrist strap to release any static electricity built up in your body.

### 1.1.3. Handling the optical pickup

- 1. In order to maintain quality during transport and before installation, both sides of the laser diode on the replacement optical pickup are shorted. After replacement, return the shorted parts to their original condition. (Refer to the text.)

- 2. Do not use a tester to check the condition of the laser diode in the optical pickup. The tester's internal power source can easily destroy the laser diode.

### 1.2. Handling the traverse unit (optical pickup)

- 1. Do not subject the traverse unit (optical pickup) to strong shocks, as it is a sensitive, complex unit.

- 2. Cut off the shorted part of the flexible cable using nippers, etc. after replacing the optical pickup. For specific details, refer to the replacement procedure in the text. Remove the anti-static pin when replacing the traverse unit. Be careful not to take too long a time when attaching it to the connector.

- 3. Handle the flexible cable carefully as it may break when subjected to strong force.

- 4. It is not possible to adjust the semi-fixed resistor that adjusts the laser power. Do not turn it

### 1.3. Cautions on removing the CD traverse unit

\* For removing the CD traverse unit in detail, refer to the "Adjustment Method" section of this manual.

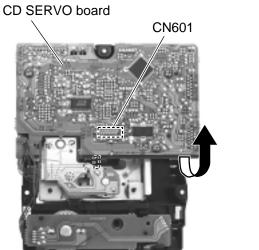

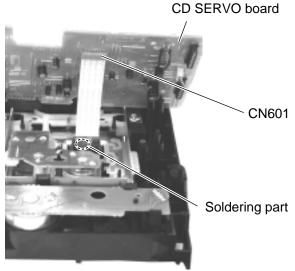

1. Before disconnecting the flexible wire from the connector CN601 on the CD SERVO board, solder the part shown in the figure below.

(Note: If the flexible wire is disconnected from the CN601 without presoldering, it may cause breakdown of the CD pickup assembly.)

2. When reassembling the CD traverse unit, be sure to remove the solder from the soldered part after reconnecting the flexible wire to the CN601.

1-5

# Important for laser products

### **1.CLASS 1 LASER PRODUCT**

- 2.DANGER : Invisible laser radiation when open and inter lock failed or defeated. Avoid direct exposure to beam.

- **3.CAUTION :** There are no serviceable parts inside the Laser Unit. Do not disassemble the Laser Unit. Replace the complete Laser Unit if it malfunctions.

- **4.CAUTION :** The compact disc player uses invisible laserradiation and is equipped with safety switches whichprevent emission of radiation when the drawer is open and the safety interlocks have failed or are de feated. It is dangerous to defeat the safety switches.

- VARNING : Osynlig laserstrålning är denna del är öppnad och spårren är urkopplad. Betrakta ej strålen.

- VARO : Avattaessa ja suojalukitus ohitettaessa olet alttiina näkymättömälle lasersäteilylle.Älä katso säteeseen.

- **5.CAUTION** : If safety switches malfunction, the laser is able to function.

- **6.CAUTION**: Use of controls, adjustments or performance of procedures other than those specified herein may result in hazardous radiation exposure.

A CAUTION Please use enough caution not to see the beam directly or touch it in case of an adjustment or operation check.

# REPRODUCTION AND POSITION OF LABELS

# **Disassembly method**

### <Main body>

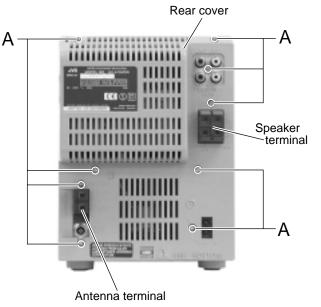

### Removing the rear cover

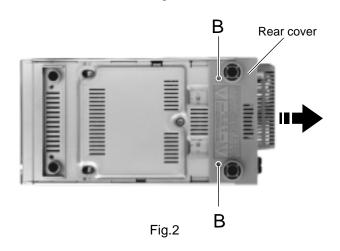

(See Fig.1 and 2)

- 1. Remove the nine screws **A** attaching the rear cover on the back of the body.

- 2. Remove the two screws **B** attaching the rear cover on the bottom of the body.

- 3. Unlock the speaker terminal and the antenna terminal, then remove the rear cover backward with releasing the hooks.

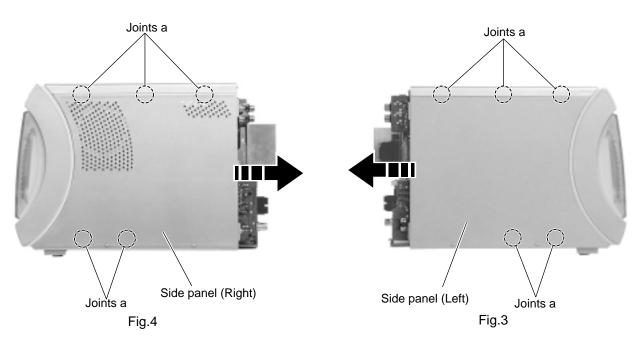

### ■ Removing the side panels (See Fig.3 and 4)

- Prior to performing the following procedure, remove the rear cover.

- 1. Remove each side panel backward while releasing the joints **a**.

Fig.1

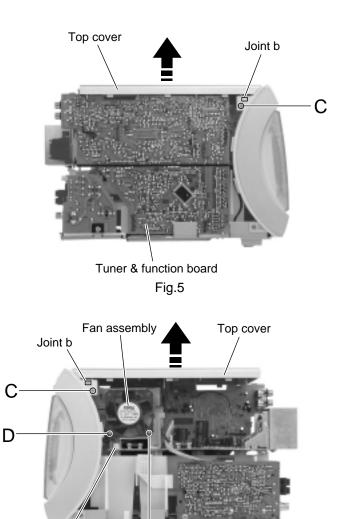

### ■Removing the top cover

(See Fig.5 and 6)

- Prior to performing the following procedure, remove the rear cover and the side panels.

- 1. Remove the two screws  ${\bm C}\,$  on each side of the body.

- 2. Release the joint **b** on each side of the body and remove the top cover backward and upward.

### Removing the fan assembly (See Fig.6)

- \*Prior to performing the following procedure, remove the rear cover, the right and left side panels.

- 1. Remove the two screws **D** on the right side of the body and pull out the fan assembly sideward.

- 2. Disconnect the wire from connector CN807 on the main board.

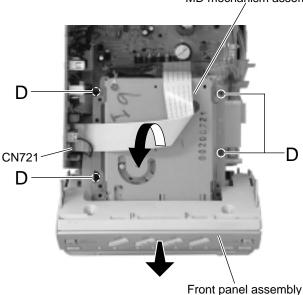

### Removing the MD mechanism assembly unit (See Fig.7)

- Prior to performing the following procedure, remove the rear cover, the side panels, the top cover and the fan assembly.

- 1. Disconnect the card wire from connector CN721 on the tuner & function board.

- 2. Remove the four screws **D** and the MD mechanism assembly backward and upward while pulling the front panel assembly forward.

D

Fig.6

CN807

MD mechanism assembly

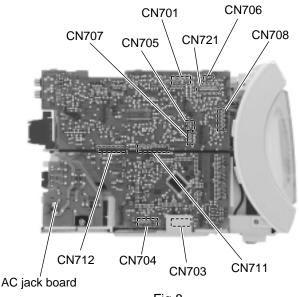

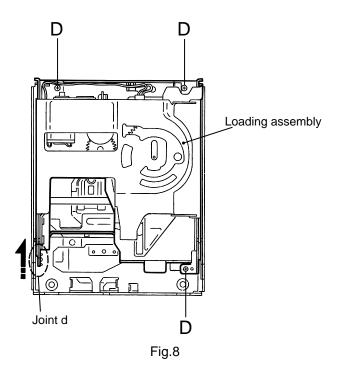

### Removing the tuner & function board (See Fig.8)

- Prior to performing the following procedure, remove the rear cover, the side panels and the top cover.

- 1. Disconnect the card wire from connector CN701, CN705, CN707, CN708 and CN721 on the tuner & function board on the right side of the body. Similarly, disconnect the harness from CN706.

- CAUTION: For the card wire connected to CN707, disconnect it after performing the following procedure 2 and 3.

- 2. Disconnect connector CN711 and CN712 on the tuner & function board from CN801 and CN802 on the main board by pulling them outward.

- 3. Disconnect connector CN703 and CN704 on the tuner & function board from CN603 and CN604 on the CD servo board by pulling them upward.

Fig.8

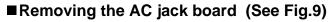

- Prior to performing the following procedure, remove the rear cover and the right side panel.

- 1. Remove the screw **E** on the right side of the body and release the AC jack board from the two joints **c**.

- 2. Disconnect the harness from connector CN805 on the AC jack board.

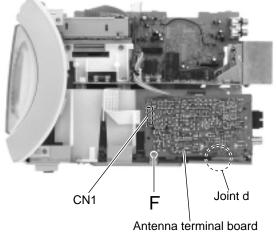

### ■Removing the antenna terminal board (See Fig.10)

- Prior to performing the following procedure, remove the rear cover and the left side panel.

- 1. Disconnect the card wire from connector CN1 on the left side of the body.

- 2. Remove the screw **F** and release the antenna terminal board from the joint **d** upward.

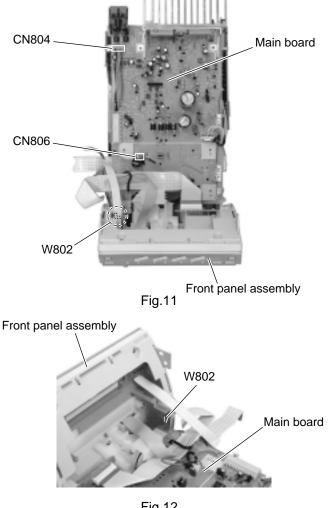

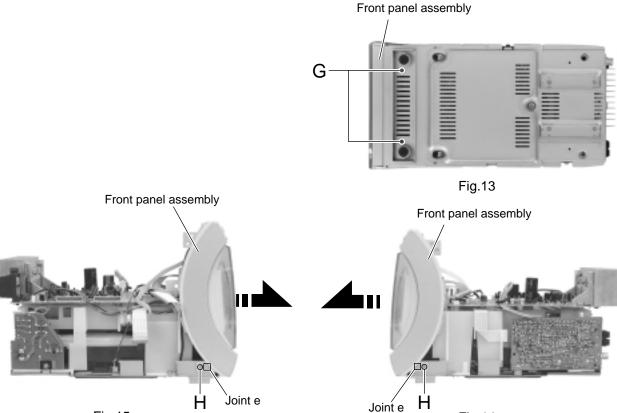

### Removing the front panel assembly unit (See Fig.11 to 15)

- · Prior to performing the following procedure, remove the rear cover, the side panels, thetop cover, the MD mechanism assembly and the tuner & function board.

- 1. Disconnect the wire from connector CN804 and CN806 on the main board. Disconnectthe wire from W802 pin terminal.

- 2. Remove the two screws G on the bottom of the body.

- 3. Remove the lower screw **H** on each side of the body.

- 4. Release the lower joint e on each side of the body. Pull out the front panel assemblytoward the front.

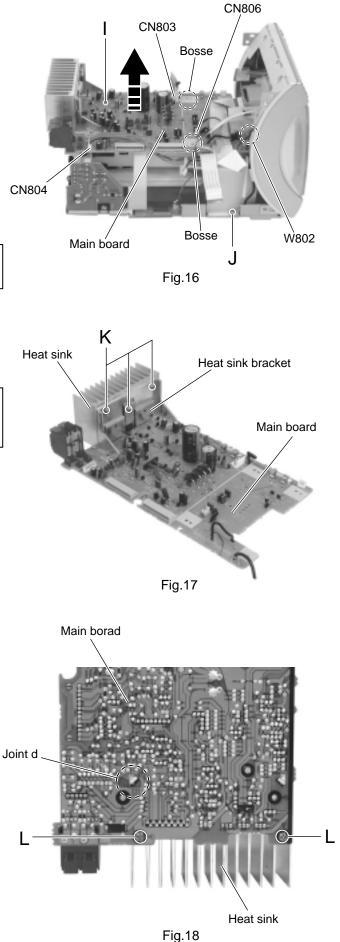

### ■Removing the main board / heat sink (See Fig.16 to 18)

- Prior to performing the following procedure, remove the rear cover, the side panels, thetop cover, the MD mechanism assembly and the tuner & function board.

- 1. Disconnect the wire from connector CN803, CN804 and CN806 on the main boardrespectively. Disconnect the wire from W802 pin terminal.

- 2.

- Remove the screw I attaching the main board and the screw J attaching the wireterminal.

CAUTION: When reasse mbling, fit the slots of the main board to the two bosses.

- 3. Remove the three screws  ${\bf K}\,$  on the heat sink bracket.

- 4. Remove the two screws L on the back of the main board.

CAUTION: When removing the heat sink bracket, disengage the two joints **d** on theback of the main board.

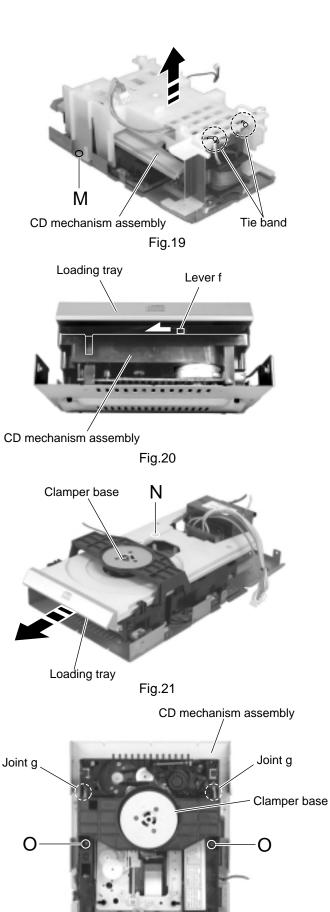

### Removing the CD mechanism assembly and the CD servo board

(See Fig.19 to 24)

- Prior to performing the following procedure, remove the rear cover, the side panels, the top cover, the MD mechanism assembly, the tuner & function board, the AC jack board, the antenna terminal board, the front panel assembly and the main board.

- 1. Cut off the two tie band on the back of the CD mechanism assembly top cover.

- 2. Remove the screw  ${\bf M}\,$  and the top cover.

- 3. Move the lever f in the direction of the arrow to draw the loading tray manually.

- 4. Remove the screw  ${\bf N}\,$  on the CD tray and pull out the CD tray from the CD mechanism assembly.

- 5. Remove the two screws  $\mathbf{O}$  attaching the clamper base on top of the CD mechanism assembly. Release the two joints  $\mathbf{g}$  with the CD mechanism assembly and remove the clamper base upward.

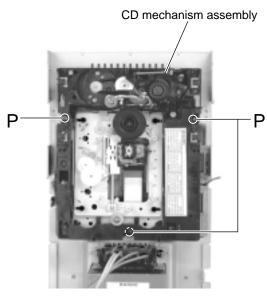

- 6. Remove the three screws **P** attaching the CD mechanism assembly.

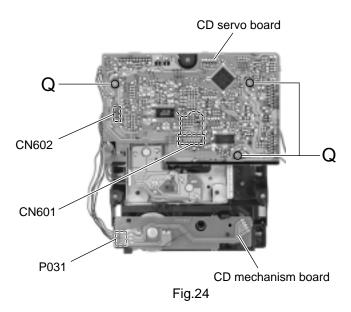

- 7. Remove the three screws **Q** attaching the CD servo board on the back of the CD mechanism assembly.

- 8. Disconnect the harness from connector P031 on the CD mechanism assembly. Disconnect the harness and the card wire from connector CN602 and CN601 on the CD servo control board respectively.

Fig.22

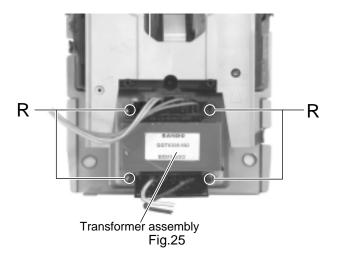

# Removing the transformer assembly (See Fig.19 and 25)

- Prior to performing the following procedure, remove the rear cover, the side panels, the top cover, the MD mechanism assembly, the tuner & function board, the AC jack board, the antenna terminal board, the front panel assembly and the main board.

- Cut off the two wire clamp on the back of the CD <sup>1.</sup> mechanism assembly upper cover.

- Remove the screw  ${\bf M}$  and the CD mechanism  $^{2\cdot}$  assembly upper cover.

Remove the four screws  ${\bf R}\,$  attaching the transformer  $^{3.}$  assembly.

### <MD mechanism assembly unit>

• Prior to performing the following procedure, remove the rear cover, the side panels, the top cover unit and the MD mechanism assembly unit.

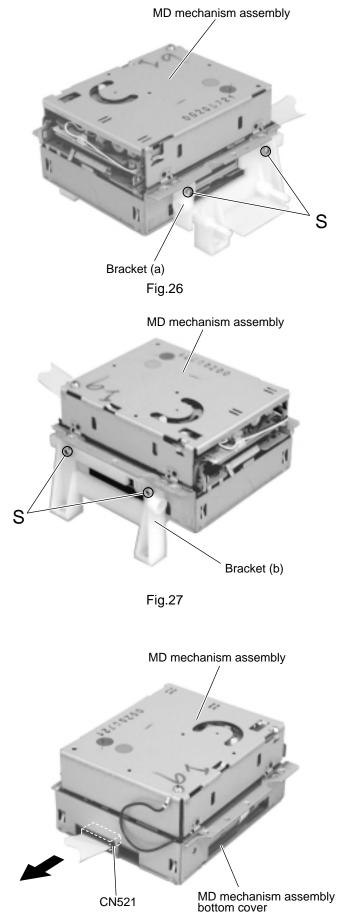

### Removing the MD mechanism assembly (See Fig.26 to 28)

- 1. Remove the four screws **S** attaching the bracket (a) and (b) on both sides of the MD mechanism assembly unit.

- 2. Disconnect the card wire from connector CN521 on the MD mechanism board. Remove the MD mechanism assembly bottom cover downward.

Fig.28

### <Front panel assembly unit>

• Prior to performing the following procedure, remove the rear cover, the side panels, the top cover, the MD mechanism assembly unit, the tuner & function board and the front panel assembly unit.

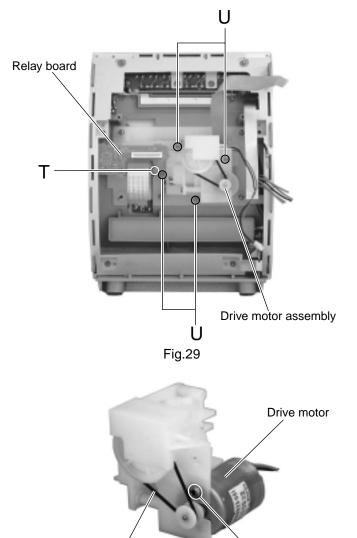

### ■Removing the relay board (See Fig.29)

- 1. Disconnect the card wire from connector CN908 on the relay board respectively.

- 2. Remove the screw  ${\bm T}$  attaching the relay board.

### ■ Removing the drive motor assembly (See Fig.29 and 30)

- 1. Remove the four screws  ${\bf U}\,$  attaching the drive motor assembly.

- 2. Remove the belt and the screw  ${\bf V}\,$  attaching the drive motor.

Fig.30

Beĺt

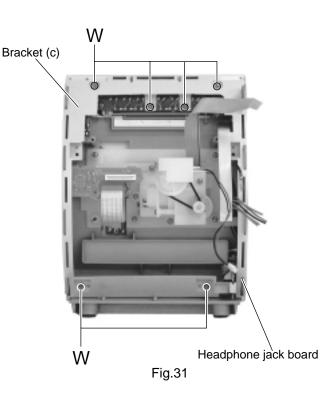

### ■Removing the headphone jack board (See Fig.31)

1. Remove the six screws  ${\bf W}\,$  attaching the bracket (c), and detach the headphone jack board.

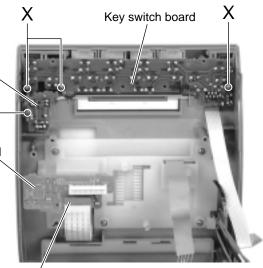

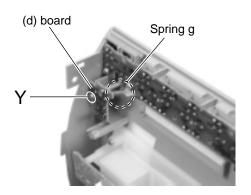

# ■Removing the key switch board / (d) board (See Fig.32 and 33)

- Prior to performing the following procedure, remove the bracket (c). (d) board

- 1. Remove the three screws  ${\bf X}\,$  attaching the key switch board.

- 2. Remove the spring g and the screw **Y** attaching the Relay board (d) board.

Fig.32

Y.

Fig.33

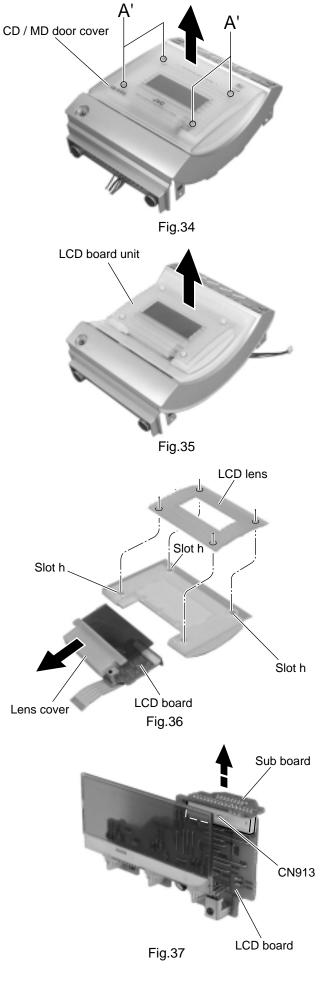

### Removing the LCD board / sub board (See Fig.32 and 34 to 37)

- 1. Disconnect the card wire from connector CN908 on the relay board on the back of thefront panel assembly.

- 2. Remove the four screws **A'** attaching the CD / MD door cover on the front side of the frontpanel assembly. Remove the CD / MD door cover, then the LCD board unit.

- 3. Pull out the LCD lens from the four bosses on the LCD board unit.

- 4. Remove the LCD board and the lens cover in the direction of the arrow (The lens cover isattached with a double-sided tape).

- 5. Disconnect the sub board from connector CN913 on the LCD board.

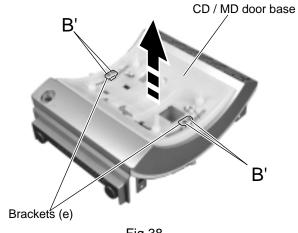

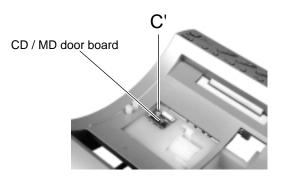

### Removing the CD / MD door board (See Fig.38 and 39)

- · Prior to performing the following procedure, remove the LCD board unit.

- 1. Remove the four screws  ${\boldsymbol B}^{\boldsymbol \prime}$  attaching the two brackets (e). Remove the CD / MD door base and the two brackets (e).

- 2. Remove the screw  $\ensuremath{\textbf{C}}\xspace$  attaching the CD / MD door board.

Fig.39

# **Disassembly method**

### <Main body>

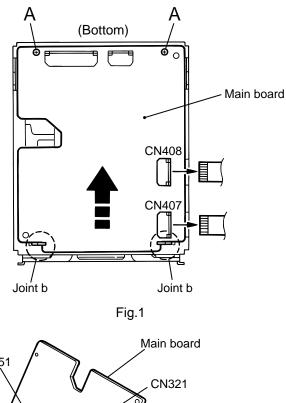

### Removing the main board (See Fig.1 and 2)

- 1. Turn over the body and disconnect the card wire from connector CN408 and the flexible wire from CN407 on the main board.

- 2. Remove the two screws A attaching the main board. Slide the main board in the direction of the arrow to release the two joints a with the single flame.

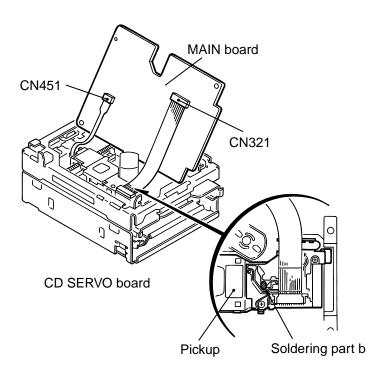

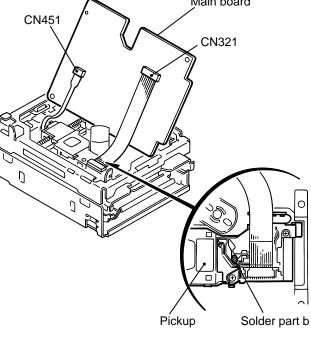

- 3. Solder part b on the pickup in the body. Disconnect the flexible harness from connector CN321 and CN451 on the underside of the main board. Then remove the main board.

Fig.2

Joint c

# Fook Joint c

### Removing the mechanism cover

(See Fig.3)

- 1. Remove the four screws B on both sides of the body.

- 2. Move the mechanism cover toward the front to disengage the front hook of the mechanism cover from the internal loading assembly (Joint c). Then remove the mechanism cover upward.

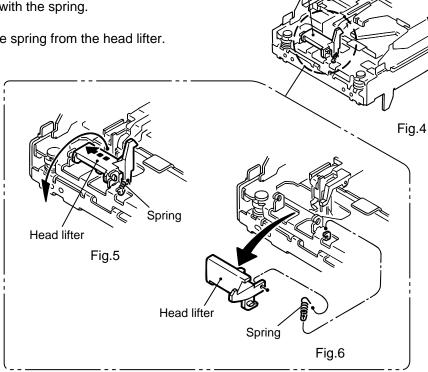

### Removing the head lifter (See Fig.4 to 6)

- 1. Move the head lifter on top of the body in the direction of the arrow and turn around.

- 2. Detach the spring from the hook of the body. Remove the head lifter with the spring.

- 3. If necessary, remove the spring from the head lifter.

Head lifter

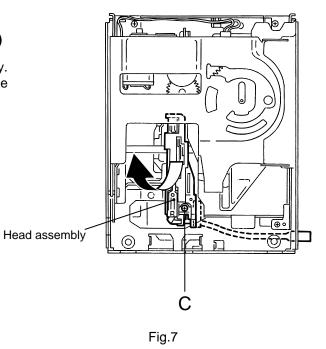

### Removing the head assembly (See Fig.7)

1. Remove the screw C on the upper side of the body. Remove the head assembly while pulling the flexible harness from the body.

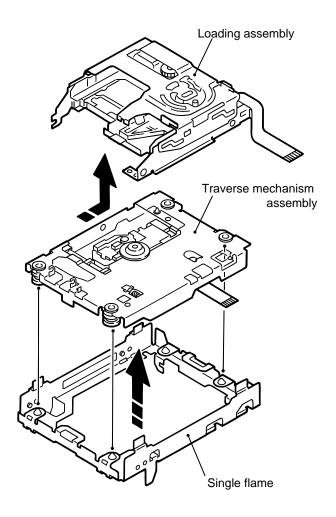

### Removing the Loading assembly (See Fig.8 and 9)

- Ref: The loading assembly, the traverse mechanism assembly and the single flame will be removable after removing the loading assembly from the body.

- Prior to performing the following procedure, remove the main board, the mechanism cover, the head lifter and the head assembly.

- 1. Remove the three screws D on the upper side of the body.

- 2. Move the loading assembly forward to disengage it from the traverse mechanism assembly (Joint d). Then remove it upward.

- 3. Remove the traverse mechanism assembly from the single flame.

### <Loading assembly>

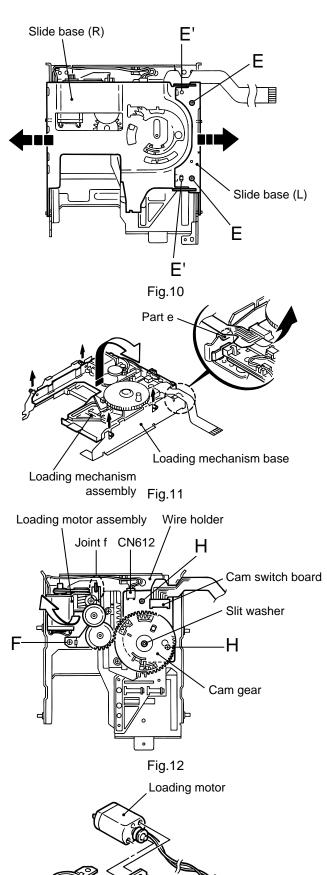

## ■Removing the slide base (L) / (R)

(See Fig.10)

- 1. Remove the two screws E on the upper side of the loading assembly.

- 2. Remove the slide base (L) outward. (Release it from the joint bosses E.)

- 3. Remove the slide base (R) outward.

Belt

Fig.13

### Removing the loading mechanism assembly (See Fig.11)

1. Detach the loading mechanism assembly upward to release the four pins on both sides from the loading motor, paying attention to the part e of the loading mechanism base.

### -Loading mechanism assembly -

### Removing the loading motor (See Fig.12 and 13)

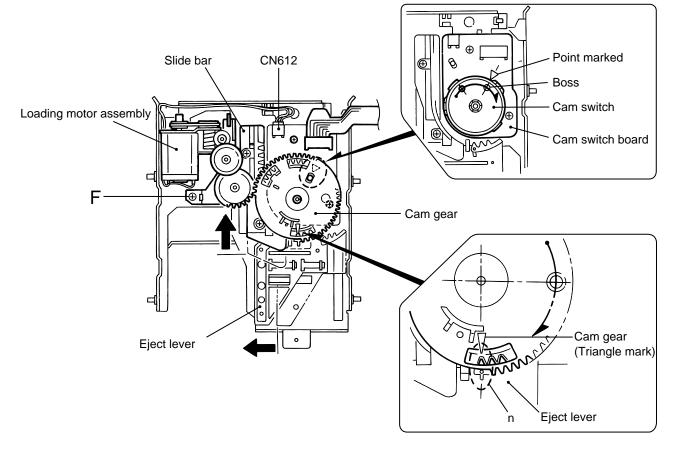

- 1. Disconnect the harnesses from the wire holder and from connector CN612 on the cam switch board.

- 2. Remove the screw F attaching the loading motor and release the joint f.

- 3. Remove the belt from the loading motor assembly.

- 4. Remove the two screws G attaching the loading motor.

# ■Removing the cam gear and the cam switch board (See Fig.12)

- 1. Remove the slit washer attaching the cam gear and pull out the cam gear.

- 2. Disconnect the harness from the wire holder and from connector CN612 on the cam switch board.

- 3. Remove the two screws H and the clamp. Remove the cam switch board.

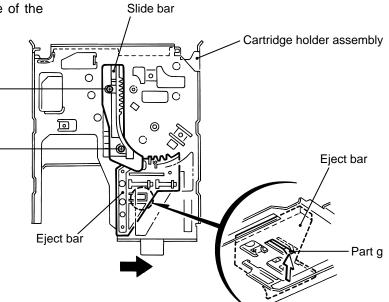

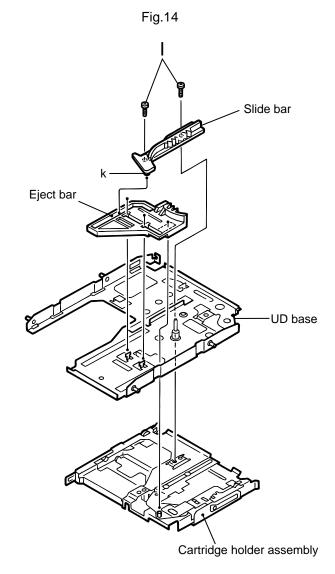

# Removing the cartridge holder assembly (See Fig.14 and 15)

1. Remove the two screws I on the upper side of the loading assembly.

### Removing the slide bar and the eject bar (See Fig.14 and 15)

- Prior to performing the following procedure, remove the cartridge holder assembly.

- 1. Remove the slide bar upward.

- 2. Move the eject bar outward until it stops as shown in Fig.14. Push the convex part g on the bottom of the body and remove the eject bar from the chassis.

### <Traverse mechanism assembly>

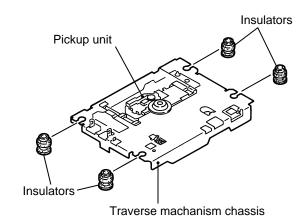

### Removing the Insulators (See Fig.16)

1. Disengage the four insulators from the notches of the traverse mechanism chassis.

Fig.16

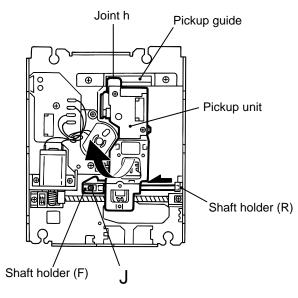

### Removing the pickup unit (See Fig.17)

- 1. Turn over the traverse mechanism assembly and remove the screw J attaching the shaft holder (F).

- 2. Move the shaft inward and remove it from the shaft holder (R).

- 3. Detach the shaft side of the pickup unit upward and release the joint h with the pickup guide. Then remove the pickup unit with the shaft.

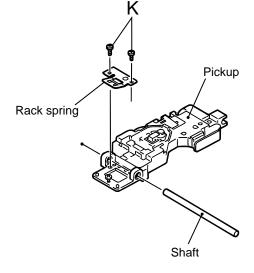

### Removing the pickup (See Fig.18)

- 1. Draw out the shaft from the pickup.

- 2. Remove the two screws K attaching the rack spring.

Ð

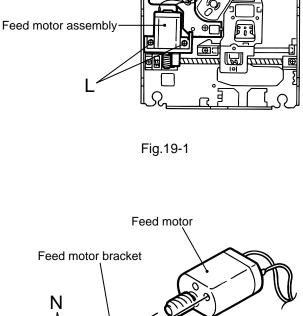

### Removing the feed motor assembly (See Fig.19-1, 19-2)

- · It is not necessary to remove the pickup unit.

- 1. For the white and black harnesses extending from the feed motor assembly, unsolder the soldering i on the traverse mechanism board.

- 2. Remove the two screws L attaching the feed motor assembly.

- 3. Remove the two screws N attaching the feed motor bracket.

### Removing the traverse mechanism board (See Fig.19-1)

- Prior to performing procedure, remove the feed motor assembly.

- 1. For the red and black harnesses extending from the spindle motor, unsolder the soldering j on the traverse mechanism board.

- 2. Remove the screw M attaching the traverse mechanism board.

Soldering j

Traberse mechanism board

M

Soldering in

Fig.19-2

### <Reattaching the loading assembly>

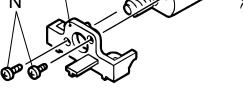

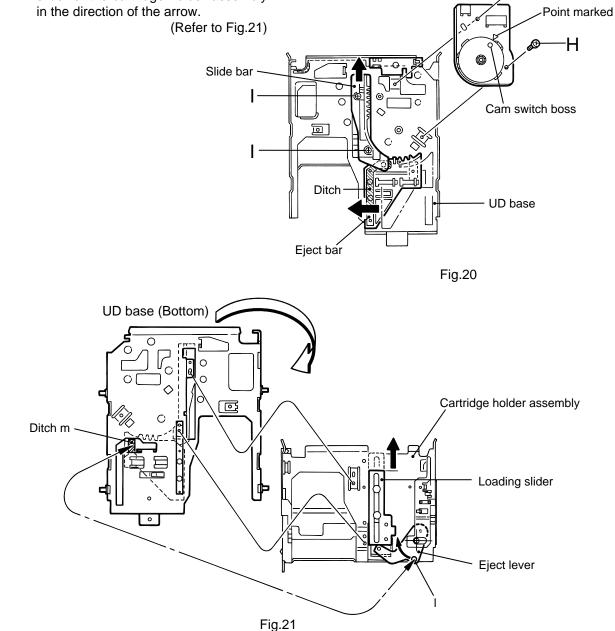

1. Reattach the eject bar to the UD base.

(Fig.15 and 20)

- 2. Reattach the slide bar to the loading mechanism chassis while fitting the boss marked k to the eject bar slot. (Fig.20)

- 3. Slide the slide bar and the eject bar in the direction of the arrow in Fig.20 and reattach the cartridge holder assembly using the two screws I.

(Fig.20 and 21)

ATTENTION: Make sure the pin of the eject lever marked I is fitted to the slot of the eject bar marked m at the bottom of the loading mechanism chassis after moving the eject lever and the loading slider of the cartridge holder assembly in the direction of the arrow.

·H

Cam switch board

1-26

- 4. Reattach the wire holder to the UD base while engaging the UD base hook marked u to the wire holder slot marked t (At the same time, the boss on the reverse side of the wire holder is fitted to the UD base round hole).

- 5. Reattach the cam switch board using the two screws H. (Fig.22)

- 6. Turn the cam switch to bring the boss to the point marked  $\triangle$  on the cam switch board. Reattach the cam gear using a slit washer while fitting the cam gear slot to the cam switch boss. (Fig.22)

- ATTENTION: When reattaching the cam gear, the cam switch boss should be fitted to the cam gear slot, and the triangle mark of the cam gear should be aligned to the hole of the eject bar as shown in Fig.22.

- Reattach the loading motor assembly, using the screw F. Connect the harness extending from the loading motor to connector CN612 on the switch board and fix it with the wire holder. (Fig.22)

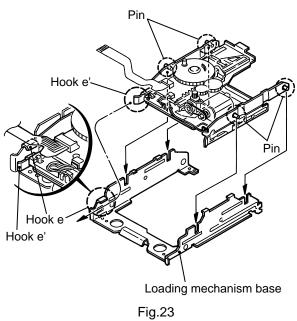

- 8. Reattach the UD base while engaging the four pins on both sides of the UD base to the notches of the loading mechanism base and placing the edge (marked e') of the cartridge holder assembly under the hook e of the loading mechanism base. (Fig.23)

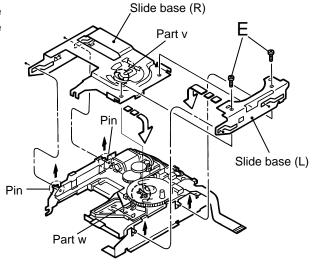

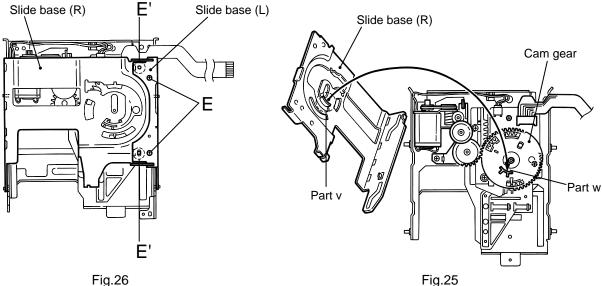

- 9. Reattach the slide base (R) while fitting the two pins on another side of the UD base to the slots of the slide base (R). (Fig.24)

- ATTENTION: Fit the part v of the slide base (R) to the part w on the inward side of the cam gear rib. (Fig.25)

- 10. Reattach the slide base (L) on the slide base (R) while fitting the two pins on another side of the UD base to the slots of the slide base (L) (Fig.25). Make sure the two slots of the slide base (L) are fitted to the two bosses marked E' and tighten the two screws E. (Fig.26)

- Ref: To expedite the work, bring up the UD base slightly when fitting each pin to the appropriate notch.

# Adjustment Method (CD/MD section)

### 1. Jigs and test instruments

Laser power meter Laser power meter sensor (or disk sensor) Premastered disk (MRG-1018) Recordable disk

2. Adjustment and check items1) Indications in the modes that all LCD's are on

### 2) CD section

- (1) Indication of the C1 error

- (2) Cancel of the C1 error indication

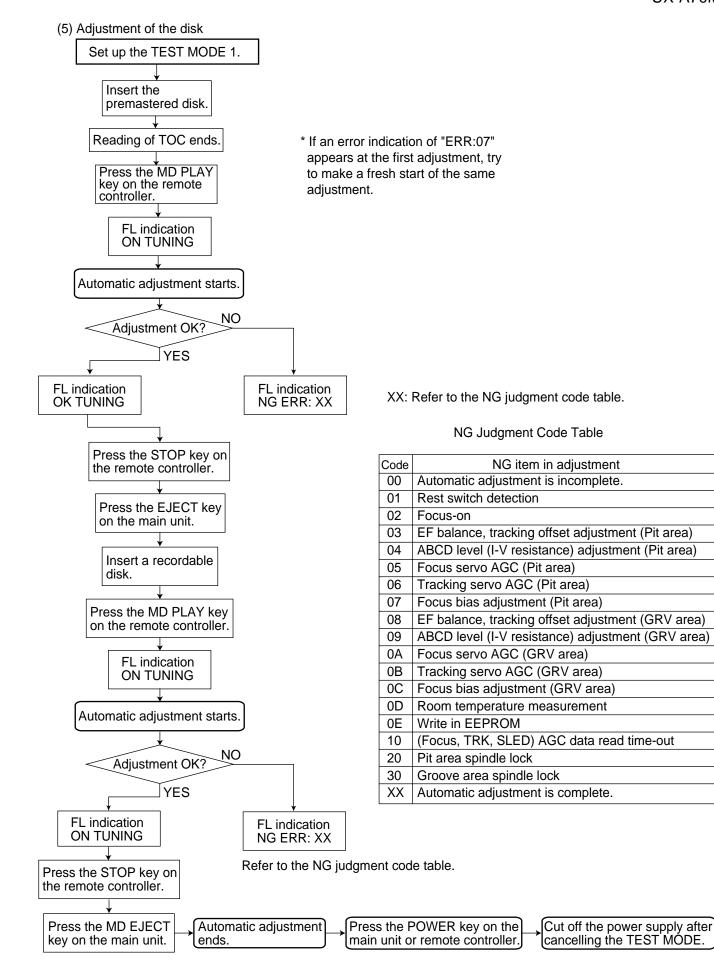

### 3) MD section

- (1) Setup of the TEST MODE 1

- (2) Initialization of the EEPROM

- (3) Adjustment of the laser power

- (4) Adjustment of the disk

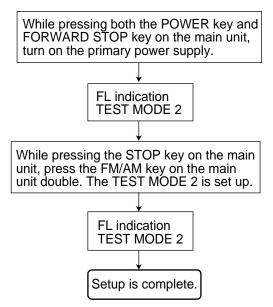

- (5) Setup of the TEST MODE 2

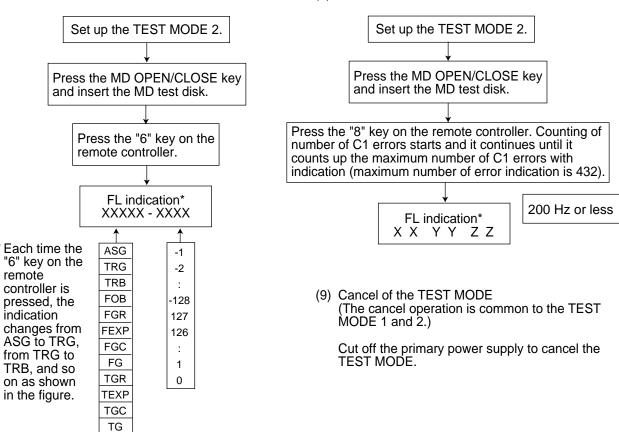

- (6) Indication of variation in the pickup adjustment value

- (7) Indication of the C1 error

- (8) Cancel of the TEST MODE

### 3. Adjustment and check method

### 1) CD section

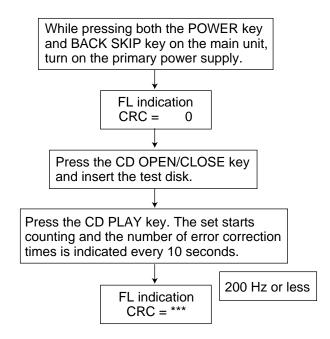

(1) Indication of the C1 error

(2) Cancel of the C1 error indication

To cancel the C1 error indication, cut off the power supply.

### 2) MD section

(1) Setup of the TEST MODE 1

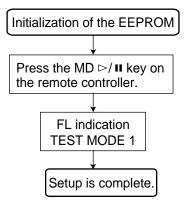

While pressing both the POWER key and FORWARD SKIP key, turn on the primary power supply. FL indication TEST MODE 1 Setup is complete. (2) Initialization of the EEPROM

(The EEPROM can be initialized on the precondition that the setup of the TEST MODE 1 is complete. After setup of the TEST MODE 1, proceed to the following operations with the remote controller\*.)

\* For EJECT operation, use the EJECT key on the main unit.

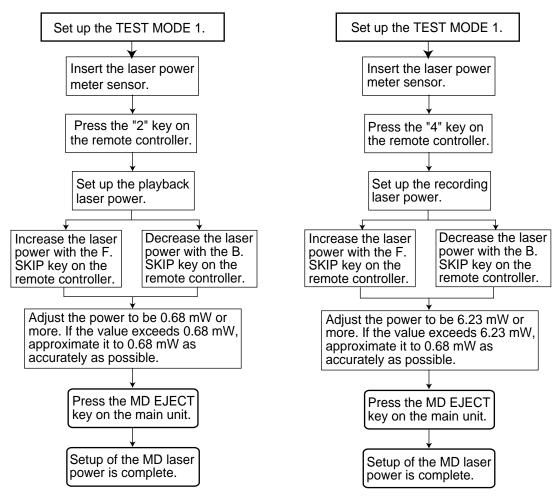

(3) Adjustment of the playback laser power

(4) Adjustment of the recording laser power

For investigating the mode in which an error occurred during the disk adjustment, freeze the set in the mode by pressing the proper key (refer to the table on the right) on the remote controller before cancelling the TEST MODE 1.

| Key to press                  | Mode               |

|-------------------------------|--------------------|

| SLEEP key (Remote controller) | FOCUS SEARCH       |

| "6" key (Remote controller)   | PIT ROUGH SERVO    |

| "7" key (Remote controller)   | GROOVE ROUGH SERVO |

| "8" key (Remote controller)   | TRACKING ON        |

| "9" key (Remote controller)   | TRACKING OFF       |

| STOP key (Remote controller)  | STOP               |

| EJECT key (Main unit)         | EJECT              |

### (6) Setup of the TEST MODE 2

(7) Indication of variation in the pickup adjustment value

### (8) Indication of the C1 error

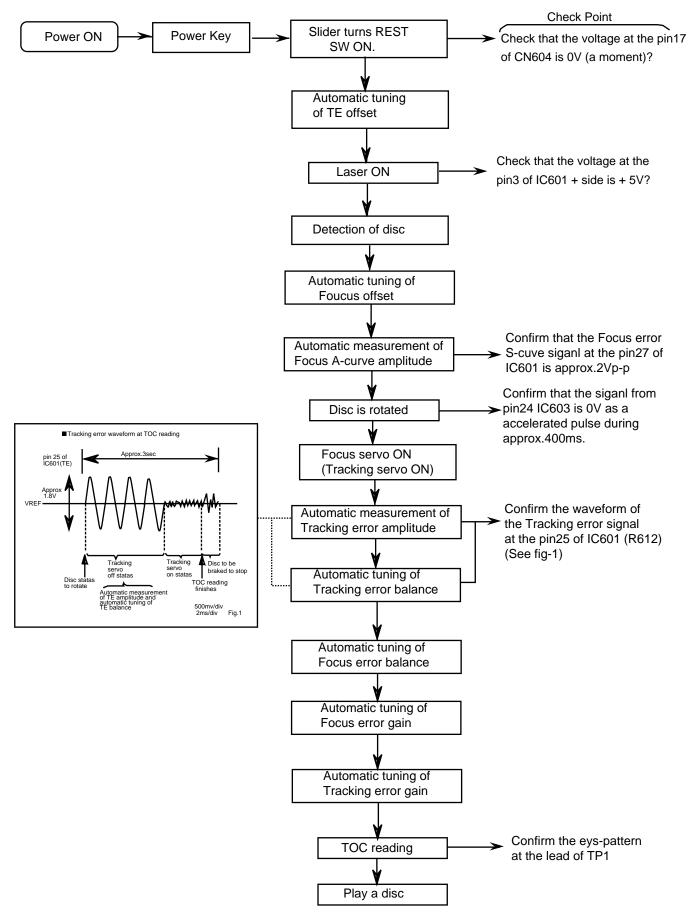

# Flow of functional operation until TOC read (CD)

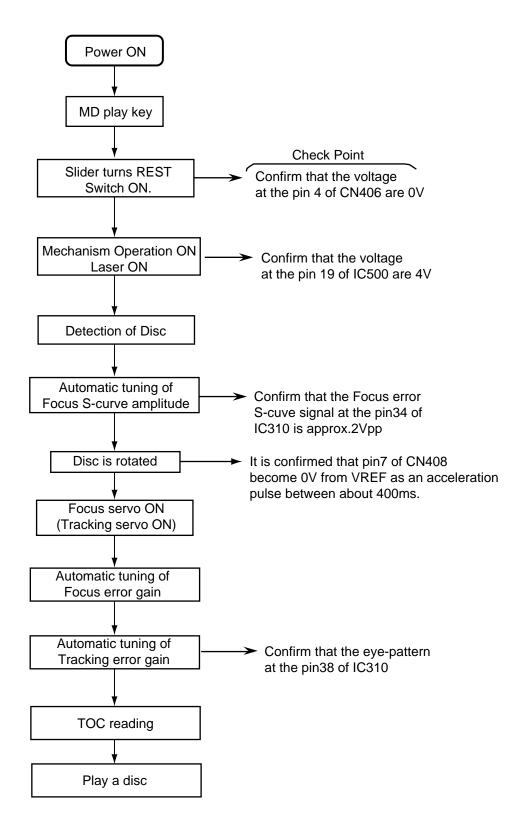

# Flow of functional operation until TOC read (MD)

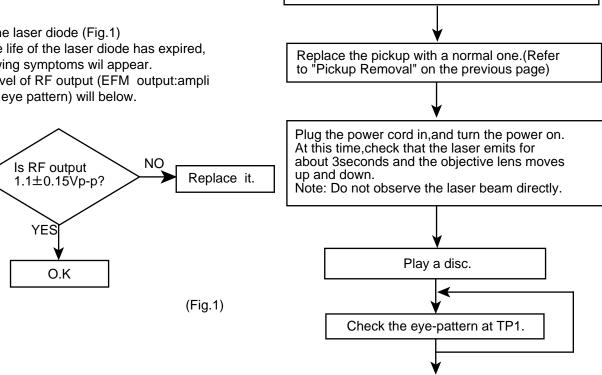

**Replacement of laser pickup**

Turn off the power switch and, disconnect the

Finish.

power cord from the ac outlet.

# Maintenance of laser pickup

- (1) Cleaning the pick up lens Befor you replace the pick up, please try to clean the lens with a alcohol soaked cotton swab.

- (2) Life of the laser diode (Fig.1) When the life of the laser diode has expired, the following symptoms wil appear.

- (1) The level of RF output (EFM output:ampli tude of eye pattern) will below.

(3) Semi-fixed resistor on the APC PC board The semi-fixed resistor on the APC printed circuit board which is attached to the pickup is used to adjust the laser power. Since this adjustment should be performed to match the characteristics of the whole optical block, do not touch the semi-fixed resistor. If the laser power is lower than the specified value, the laser diode is almost worn out, and the laser pickup should be replaced. If the semi-fixed resistor is adjusted while the pickup is functioning normally, the laser pickup may be damaged due to excessive current.

# Maintenance of MD pickup

### 1. Cleaning of pickup lens

- (1) Prior to changing the pickup, clean the pickup lens.

- (2) For cleaning the lens, use the following cotton swab after mearsing it in alcohol.

Product No. JCB-B4; Manufacturer; Nippon Cotton Swab

- Confirmation of the service life of laser diode when the service life of the laser diode has been exhausted, the following symptoms will appear.

- (1) Recording will become impossible.

- (2) The RF output (EFM output and eye pattern amplitude) will become lower.

- (3) The drive current required for light emitting of laser diode will be increased.

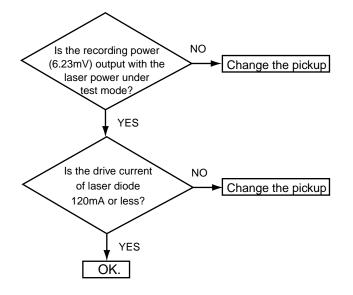

Confirm the service life according to the following flow chart:

# 3. Method of measuring the drive current of laser diode

When the voltage measured at TP ILCC (Q301 emitter) and +5V (Q303 emitter) of the MD servo P.C. board (ENX-0223) have become 600mV or over, the service life of the laser diode is judged to have been exhausted.

| [Caution] When TP ILCC (Q301 collector) and |

|---------------------------------------------|

| +5V (Q303 emitter have been is short        |

| circuit on such an occasion, then the       |

| laser diode will be broken. Therefore,      |

| take utmost care in handling the MD         |

| pickup.                                     |

|                                             |

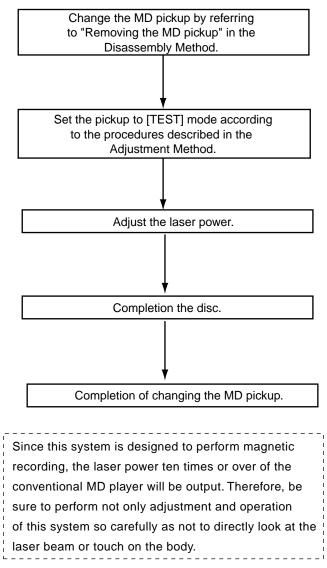

# **Procedures of changing the MD pickup**

# 4. Semi-solid state resistors on the APC P.C. board

The semi-solid state resistor on the APC P.C.board attached to the pickup is used for adjusting the laser power. Since these resistor should be adjusted in pair according to the characteristics of the optical block, be sure not to touch on the resistors.

Since the service life of the laser diode will be exhausted when the laser power is low, it is necessary to change the pickup. Meanwhile, do not pickup. Otherwise, the pickup will be damaged due to over current.

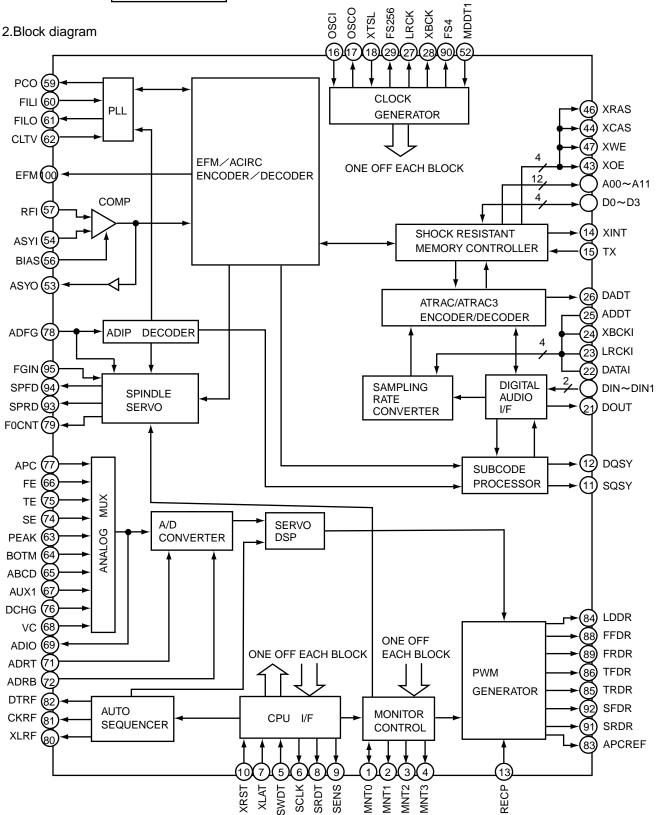

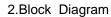

# **Description of major ICs**

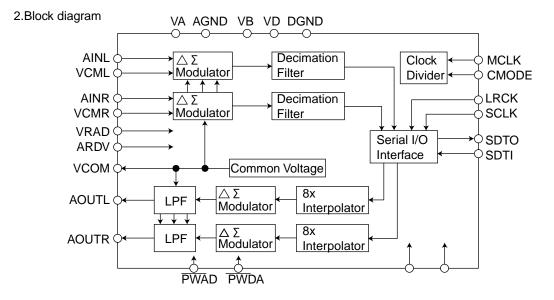

AK4519VF-X (IC480) : A / D D / A converter

1.Pin layout

#### 3.Pin Function

| Pin<br>NO. | ,     | I/O | Function                                |

|------------|-------|-----|-----------------------------------------|

| 1          | VRDA  | 1   | Voltage Reference Input Pin for DAC, VA |

| 2          | VRAD  | Ι   | Voltage Reference Input Pin for ADC, VA |

| 3          | AINR  | Ι   | RCH Analog Input Pin                    |

| 4          | VCMR  | 0   | Rch Common Voltage Output Pin, 0.45xVA  |

| 5          | VCML  | 0   | Lch Common Voltage Output Pin, 0.45xVA  |

| 6          | AINL  | Ι   | Lch Analog Input Pin                    |

| 7          | PWAD  | Ι   | ADC Power-Down Mode Pin "L":Power Down  |

| 8          | PWDA  | Ι   | DAC Power-Down Mode Pin "L":Power Down  |

| 9          | MCLK  | Ι   | Master Clock Input Pin                  |

| 10         | LRCK  | Ι   | Input/Output Channel Clock Pin          |

| 11         | SCLK  | Ι   | Audio Serial Data Clock Pin             |

| 12         | SDTO  | 0   | Audio Serial Data Output Pin            |

| 13         | DGND  | -   | Digital Ground Pin                      |

| 14         | VD    | -   | Digital Power Supply Pin                |

| 15         | SDTI  | Ι   | Audio Serial Data Input Pin             |

| 16         | CMODE | Ι   | Master Clock Select Pin                 |

| 17         | DEM1  | Ι   | De-emphasis Frequency Select Pin        |

| 18         | DEM0  |     | De-emphasis Frequensy Select Pin        |

| 19         | AOUTL | 0   | Lch Analog Output Pin                   |

| 20         | AOUTR | 0   | Rch Analog Output Pin                   |

| 21         | VCOM  | 0   | Common Voltage Output Pin, 0.45xVA      |

| 22         |       |     | Analog Ground Pin                       |

| 23         | VB    |     |                                         |

| 24         | VA    | -   | Analog Power Supply Pin                 |

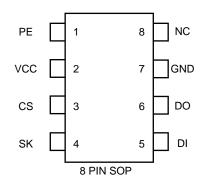

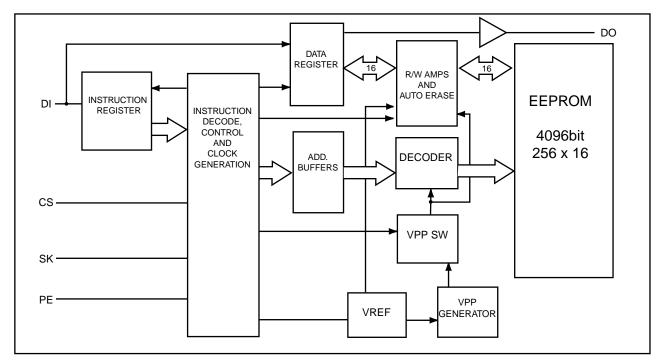

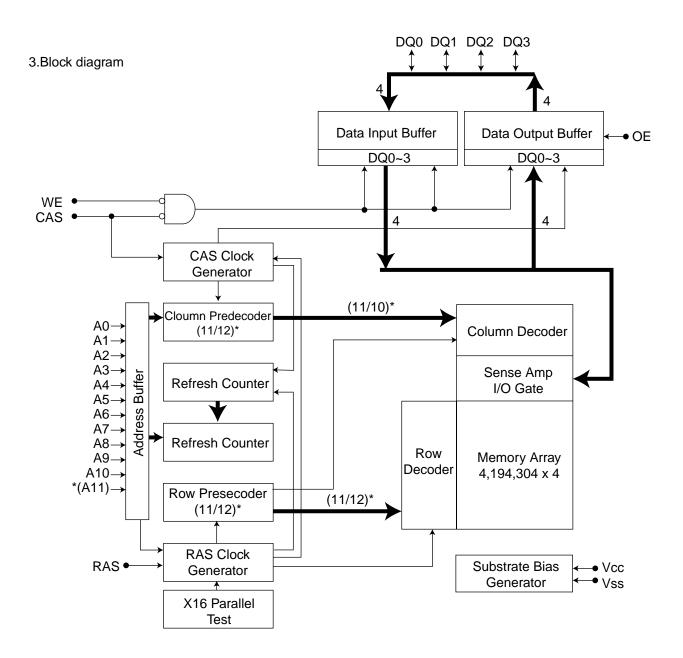

# ■ AK93C65AF-X (IC590) : EEPROM

#### 2.Block diagram

#### 3.Pin function

| Pin no. | Symbol | Function                                        |

|---------|--------|-------------------------------------------------|

| 1       | PE     | Program enable (With built-in pull-up resistor) |

| 2       | VCC    | Power supply                                    |

| 3       | CS     | Chip selection                                  |

| 4       | SK     | Cereal clock input                              |

| 5       | DI     | Cereal data input                               |

| 6       | DO     | Cereal data output                              |

| 7       | GND    | Ground                                          |

| 8       | NC     | No connection                                   |

NOTE : The pull-up resistor of the PE pin is about 2.5M  $\ensuremath{\Omega}$  (VCC=5V)

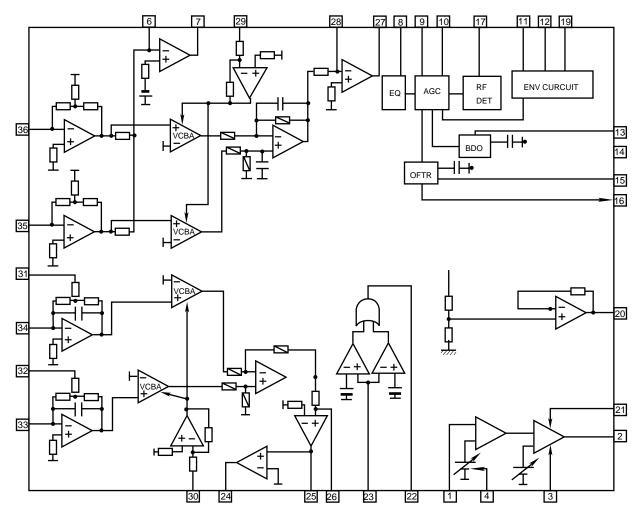

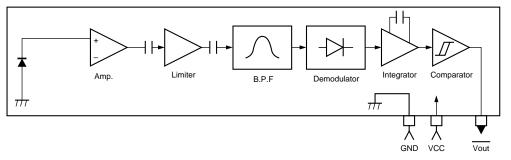

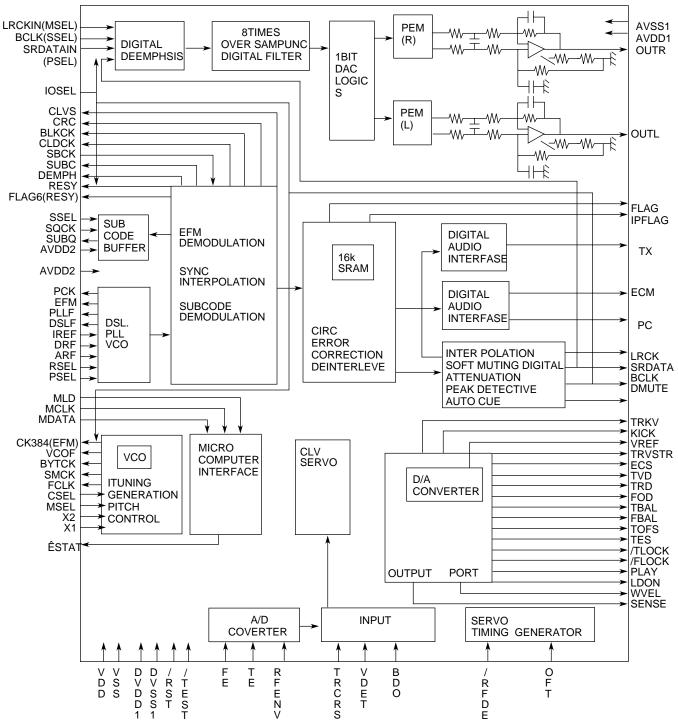

# AN8806SB-W (IC601) : RF&Servo AMP

1.Pin layout

| PD      | 1  | $\bigcirc$ | 36 | PDAC   |

|---------|----|------------|----|--------|

| LD      | 2  |            | 35 | PDBD   |

| LDON    | 3  |            | 34 | PDF    |

| LDP     | 4  |            | 33 | PDE    |

| VCC     | 5  |            | 32 | PDER   |

| RF-     | 6  |            | 31 | PDFR   |

| RF OUT  | 7  |            | 30 | TBAL   |

| RF IN   | 8  |            | 29 | FBAL   |

| C.AGC   | 9  |            | 28 | EF-    |

| ARF     | 10 |            | 27 | EF OUT |

| C.ENV   | 11 |            | 26 | TE-    |

| C.EA    | 12 |            | 25 | TE OUT |

| CS BDO  | 13 |            | 24 | CROSS  |

| BDO     | 14 |            | 23 | TE BPF |

| CS BRT  | 15 |            | 22 | VDET   |

| OFTR    | 16 |            | 21 | LD OFF |

| /NRFDET | 17 |            | 20 | VREF   |

| GND     | 18 |            | 19 | ENV    |

2.Block diagram

#### 3. Pin function

| Pin No. | Symbol  | I/O | Function                                                                      |

|---------|---------|-----|-------------------------------------------------------------------------------|

| 1       | PD      | I   | APC amp input terminal                                                        |

| 2       | LD      | 0   | APC amp output terminal                                                       |

| 3       | LD ON   | I   | APC ON/OFF control terminal                                                   |

| 4       | LDP     |     | Connect to ground                                                             |

| 5       | VCC     |     | Power supply                                                                  |

| 6       | RF-     | Ι   | Inverse input pin for RF amp                                                  |

| 7       | RF OUT  | 0   | RFamp output                                                                  |

| 8       | RF IN   | I   | RF input                                                                      |

| 9       | C.AGC   | I/O | Connecting pin of AGC loop filter                                             |

| 10      | ARF     | 0   | RF output                                                                     |

| 11      | C.ENV   | I/O | A capacitor is connected to this terminal to detect the envelope of RF signal |

| 12      | C.EA    | I/O | A capacitor is connected to this terminal to detect the envelope of RF signal |

| 13      | CS BDO  | I/O | A capacitor is connected to detect the lower envelope of RF signal            |

| 14      | BDO     | 0   | BDO output pin                                                                |

| 15      | CS BRT  | I/O | A capacitor is connected to detect the lower envelope of RF signal            |

| 16      | OFTR    | 0   | Of-track status signal output                                                 |

| 17      | /NRFDET | 0   | RF detection signal output                                                    |

| 18      | GND     |     | Ground                                                                        |

| 19      | ENV     | 0   | Envelope output                                                               |

| 20      | VREF    | 0   | Reference voltage output                                                      |

| 21      | LD OFF  |     | Connect to ground                                                             |

| 22      | VDET    | 0   | Vibration detection signal output                                             |

| 23      | TE BPF  | Ι   | Input pin of tracking error through BPF                                       |

| 24      | CROSS   | 0   | Tracking error cross output                                                   |

| 25      | TE OUT  | 0   | Tracking error signal output                                                  |

| 26      | TE-     | I   | Inverse input pin for tracking error amp                                      |

| 27      | FE OUT  | 0   | Output pin of focus error                                                     |

| 28      | FE-     | I   | Inverse input pin for focus error amp                                         |

| 29      | FBAL    | 1   | Focus balance control                                                         |

| 30      | TBAL    | I   | Tracking balance control                                                      |

| 31      | PDFR    | I/O | F I-V amp gain control                                                        |

| 32      | PDER    | I/O | E I-V amp gain control                                                        |

| 33      | PDF     | Ι   | I-V amp input                                                                 |

| 34      | PDE     | 1   | I-V amp input                                                                 |

| 35      | PD BD   | I   | I-V amp input                                                                 |

| 36      | PD AC   | Ι   | I-V amp input                                                                 |

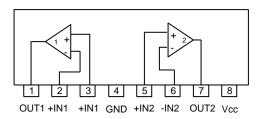

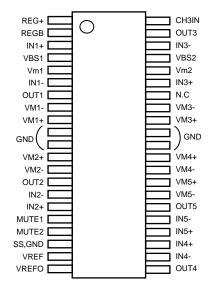

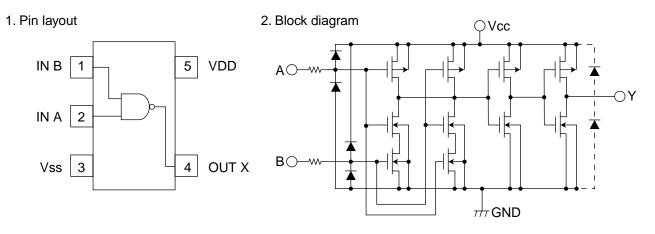

■ BA15218N (IC32 / IC35) : Dual Ope. Amp.

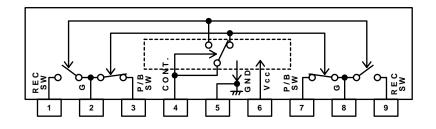

# ■BA3126N(IC31) : R/P Switch

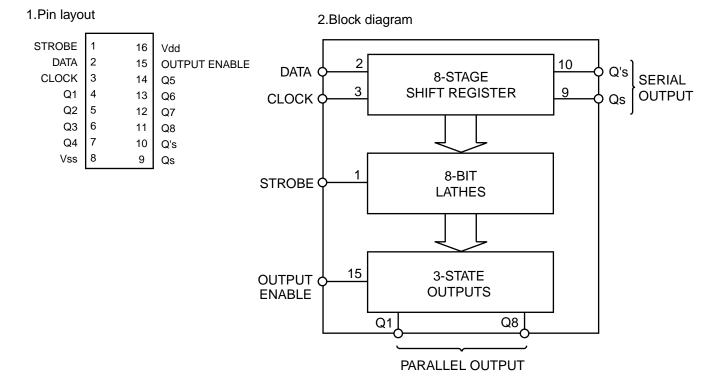

### ■ BU4094B(IC811):Serial to parallel port extension

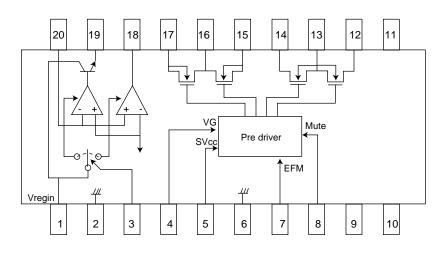

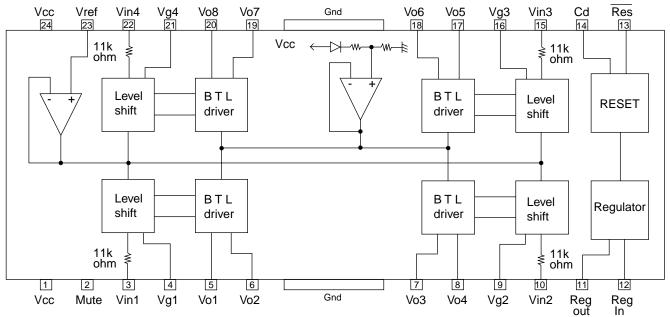

# BD7910FV-X (IC450) : Pre driver

#### 1.Block diagram

#### 2.Pin function

| Pin<br>No. | Symbol  | I/O | Function                          | Pin<br>No. | Symbol  | I/O | Function                                  |

|------------|---------|-----|-----------------------------------|------------|---------|-----|-------------------------------------------|

| 1          | Vreg IN | Т   | Regulator input and regulator     | 11         | NC      | -   | Non connect                               |

|            |         |     | power supply                      | 12         | VOD2    | 0   | Sync.output (Lower power MOS,drain)       |

| 2          | Reg GN  | -   | Regulator GND                     | 13         | VSS     | -   | "H"bridge GND (Lower power MOS,source)    |

| 3          | NC      | -   | Non connect                       | 14         | VOD1    | 0   | Sync.output (Lower power MOS,drain)       |

| 4          | VG      | Т   | Voltage input for power MOS drive | 15         | VOS1    | 0   | Source output (Upper power MOS,source)    |

| 5          | SVCC    | 0   | EFM high level output voltage     | 16         | VDD     | -   | "H" bridge power supply terminal          |

| 6          | PDGND   | -   | Pre-driver GND                    |            |         |     | (Upper power MOS,source)                  |

| 7          | EFM     | Ι   | EFM signal input                  | 17         | VOS2    | 0   | Source output (Upper power MOS,source)    |

| 8          | MUTE    | Т   | Mute control (Low active)         | 18         | Reg DRV | 0   | External PNP drive output for regulator   |

| 9          | NC      | 0   | Non conncet                       | 19         | Reg OUT | 0   | Reglator output (Emitter follower output) |

| 10         | NC      | 0   | Non connect                       | 20         | Reg NF  | -   | Regulator feedbaack terminal              |

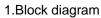

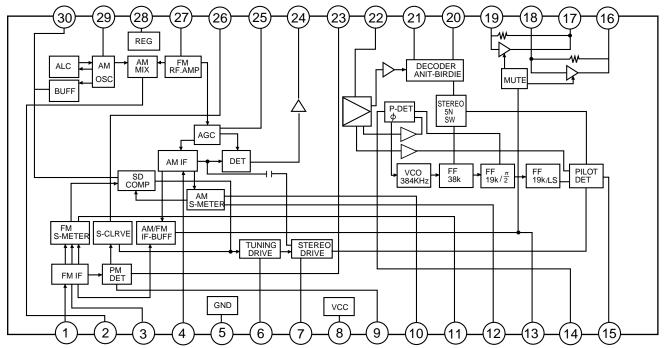

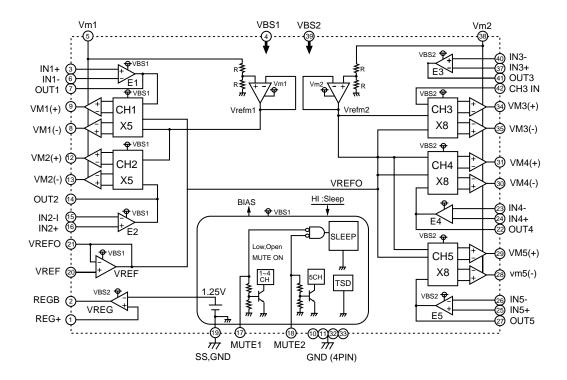

# CXA2523AR (IC310) : MD servo

#### 2.Pin function

| Pin No. | Symbol | I/O | Function                                                                |

|---------|--------|-----|-------------------------------------------------------------------------|

| 1       | I      | Ι   | I-V converted RF signal I input.                                        |

| 2       | J      | Ι   | I-V converted RF signal J input.                                        |

| 3       | VC     | 0   | Vcc/2 voltage output.                                                   |

| 4       | А      | Ι   | A current input for main beam servo signal.                             |

| 5       | В      | Ι   | B current input for main beam servo signal.                             |

| 6       | С      | Ι   | C current input for main beam servo signal.                             |

| 7       | D      | Ι   | D current input for main beam servo signal.                             |

| 8       | Е      | Ι   | E current input for side beam servo signal.                             |

| 9       | F      | Ι   | F current input for side beam servo signal.                             |

| 10      | PD     | Ι   | Reflection light quantity monitor signal input.                         |

| 11      | APC    | 0   | Laser APC output.                                                       |

| 12      | APCREF | Ι   | Reference voltage input for the laser power intensity setting.          |

| 13      | GND    | -   | Connect to GND.                                                         |

| 14      | TEMPI  | Ι   | Connects the temperature sensor.                                        |

| 15      | TEMP R | Ι   | Connects the temperature sensor. outputs the reference voltage.         |

| 16      | SWDT   | Ι   | Data input for microcomputer serial interface.                          |

| 17      | SCLK   | Ι   | Shift clock input for microcomputer serial interface.                   |

| 18      | XLAT   | Ι   | Latch signal input for microcomputer serial interface.Latched when low. |

| 19      | XSTBY  | Ι   | Standby setting pin. Normal operation when high Standby when low.       |

| 20      | F0CNT  | Ι   | Internal current source setting pin.                                    |

| 21       VREF       O       Reference voltage output.         22       EQADJ       I/O       Equalizer center frequency setting pin.         23       3TADJ       I/O       BPF3T center frequency setting pin.         24       Vcc       -       Power supply.         25       WBLADJ       I/O       BPF22 center frequency setting pin.         26       TE       O       Tracking error signal output.         27       CSLED       -       Connects the sled error signal LPF capacitor.         28       SE       O       Sled error signal output.         29       ADFM       O       ADIP FM signal output.         30       ADIN       I       ADIP signal comparator input.         31       ADAGC       -       Connects the ADIPAGC capacitor.         32       ADFG       O       ADIP2 binary value signal output.         33       AUX       O       13 output / temperature signal output. Switched with serial commands.         34       FE       O       Focus error signal output.       .         35       ABCD       O       Reflection light quantity signal output for the main beam servo detector.         36       BOTM       O       RF/ABCD bottom hold signal output.       . | Pin No. | Symbol | I/O | Function                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|-----|---------------------------------------------------------------------------|

| 23       3TADJ       I/O       BPF3T center frequency setting pin.         24       Vcc       -       Power supply.         25       WBLADJ       I/O       BPF22 center frequency setting pin.         26       TE       O       Tracking error signal output.         27       CSLED       -       Connects the sled error signal LPF capacitor.         28       SE       O       Sled error signal output.         29       ADFM       O       ADIP FM signal output.         30       ADIN       I       ADIP signal comparator input.         31       ADAGC       -       Connects the ADIPAGC capacitor.         32       ADFG       O       ADIP2 binary value signal output.         33       AUX       O       13 output / temperature signal output.         34       FE       O       Focus error signal output.         35       ABCD       O       Reflection light quantity signal output for the main beam servo detector.         36       BOTM       O       RF/ABCD bottom hold signal output.         37       PEAK       O       Peak hold signal output for the RF/ABCD signals.         38       RF       O       RF equalizer output.         39       RFAGC       -                  | 21      | VREF   | 0   | Reference voltage output.                                                 |

| 24       Vcc       Power supply.         25       WBLADJ       I/O       BPF22 center frequency setting pin.         26       TE       O       Tracking error signal output.         27       CSLED       -       Connects the sled error signal LPF capacitor.         28       SE       O       Sled error signal output.         29       ADFM       O       ADIP FM signal output.         30       ADIN       I       ADIP signal comparator input.         31       ADAGC       -       Connects the ADIPAGC capacitor.         32       ADFG       O       ADIP z binary value signal output.         33       AUX       O       13 output / temperature signal output. Switched with serial commands.         34       FE       O       Focus error signal output.         35       ABCD       O       Reflection light quantity signal output for the main beam servo detector.         36       BOTM       O       RF/ABCD bottom hold signal output.         37       PEAK       O       Peak hold signal output for the RF/ABCD signals.         38       RF       O       RF equalizer output.         39       RFAGC       -       Connects the RFAGC capacitor.         41       COMPO          | 22      | EQADJ  | I/O | Equalizer center frequency setting pin.                                   |

| 25WBLADJI/OBPF22 center frequency setting pin.26TEOTracking error signal output.27CSLED-Connects the sled error signal LPF capacitor.28SEOSled error signal output.29ADFMOADIP FM signal output.30ADINIADIP signal comparator input.31ADAGC-Connects the ADIPAGC capacitor.32ADFGOADIP2 binary value signal output.33AUXO13 output / temperature signal output. Switched with serial commands.34FEOFocus error signal output.35ABCDOReflection light quantity signal output for the main beam servo detector.36BOTMORF/ABCD bottom hold signal output.37PEAKOPeak hold signal output.38RFORF equalizer output.39RFAGC-Connects the RFAGC capacitor.40AGCIIRFAGC input.41COMPOOUser comparator output.42COMPPIUser comparator output.43ADDCI/OConnects the capacitor for ADIP amplifier feedback circuit.44OPOOUser operational amplifier output.45OPNIUser operational amplifier inverted input.46RFOORF amplifier output. Eye pattern checkpoint.47MORFIIInput of the groove RF signal with AC coupling.                                                                                                                                                                                                      | 23      | 3TADJ  | I/O | BPF3T center frequency setting pin.                                       |

| 26       TE       O       Tracking error signal output.         27       CSLED       -       Connects the sled error signal LPF capacitor.         28       SE       O       Sled error signal output.         29       ADFM       O       ADIP FM signal output.         30       ADIN       I       ADIP signal comparator input.         31       ADAGC       -       Connects the ADIPAGC capacitor.         32       ADFG       O       ADIP2 binary value signal output.         33       AUX       O       13 output / temperature signal output.         34       FE       O       Focus error signal output.         35       ABCD       O       Reflection light quantity signal output for the main beam servo detector.         36       BOTM       O       RF/ABCD bottom hold signal output.         37       PEAK       O       Peak hold signal output for the RF/ABCD signals.         38       RF       O       RF equalizer output.         39       RFAGC       -       Connects the RFAGC capacitor.         40       AGCI       I       RFAGC input.         41       COMPO       O       User comparator non-inverted input.         43       ADDC       I/O                            | 24      | Vcc    | -   | Power supply.                                                             |

| 27CSLED-Connects the sled error signal LPF capacitor.28SEOSled error signal output.29ADFMOADIP FM signal output.30ADINIADIP signal comparator input.31ADAGC-Connects the ADIPAGC capacitor.32ADFGOADIP2 binary value signal output.33AUXO13 output / temperature signal output. Switched with serial commands.34FEOFocus error signal output.35ABCDOReflection light quantity signal output for the main beam servo detector.36BOTMORF/ABCD bottom hold signal output.37PEAKOPeak hold signal output for the RF/ABCD signals.38RFORF equalizer output.39RFAGC-Connects the RFAGC capacitor.40AGCIIRFAGC input.41COMPOOUser comparator output.42COMPPIUser comparator non-inverted input.43ADDCI/OConnects the capacitor for ADIP amplifier feedback circuit.44OPOOUser operational amplifier output.45OPNIUser operational amplifier inverted input.46RFOORF amplifier output. Eye pattern checkpoint.47MORFIIInput of the groove RF signal with AC coupling.                                                                                                                                                                                                                                                  | 25      | WBLADJ | I/O | BPF22 center frequency setting pin.                                       |

| 28SEOSled error signal output.29ADFMOADIP FM signal output.30ADINIADIP signal comparator input.31ADAGC-Connects the ADIPAGC capacitor.32ADFGOADIP2 binary value signal output.33AUXO13 output / temperature signal output. Switched with serial commands.34FEOFocus error signal output.35ABCDOReflection light quantity signal output for the main beam servo detector.36BOTMORF/ABCD bottom hold signal output.37PEAKOPeak hold signal output for the RF/ABCD signals.38RFORF equalizer output.39RFAGC-Connects the RFAGC capacitor.40AGCIIRFAGC input.41COMPOOUser comparator output.42COMPPIUser comparator output.43ADDCI/OConnects the capacitor for ADIP amplifier feedback circuit.44OPOOUser operational amplifier output.45OPNIUser operational amplifier inverted input.46RFOORF amplifier output. Eye pattern checkpoint.47MORFIIInput of the groove RF signal with AC coupling.                                                                                                                                                                                                                                                                                                                   | 26      | TE     | 0   | Tracking error signal output.                                             |

| 29ADFMOADIP FM signal output.30ADINIADIP signal comparator input.31ADAGC-Connects the ADIPAGC capacitor.32ADFGOADIP2 binary value signal output.33AUXO13 output / temperature signal output. Switched with serial commands.34FEOFocus error signal output.35ABCDOReflection light quantity signal output for the main beam servo detector.36BOTMORF/ABCD bottom hold signal output.37PEAKOPeak hold signal output for the RF/ABCD signals.38RFORF equalizer output.39RFAGC-Connects the RFAGC capacitor.40AGCIIRFAGC input.41COMPOOUser comparator output.43ADDCI/OConnects the capacitor for ADIP amplifier feedback circuit.44OPOOUser operational amplifier output.45OPNIUser operational amplifier inverted input.46RFOORF amplifier output. Eye pattern checkpoint.47MORFIIInput of the groove RF signal with AC coupling.                                                                                                                                                                                                                                                                                                                                                                                | 27      | CSLED  | -   | Connects the sled error signal LPF capacitor.                             |

| 30ADINIADIP signal comparator input.31ADAGC-Connects the ADIPAGC capacitor.32ADFG0ADIP2 binary value signal output.33AUX013 output / temperature signal output. Switched with serial commands.34FE0Focus error signal output.35ABCD0Reflection light quantity signal output for the main beam servo detector.36BOTM0RF/ABCD bottom hold signal output.37PEAK0Peak hold signal output for the RF/ABCD signals.38RF0RF equalizer output.39RFAGC-Connects the RFAGC capacitor.40AGCIIRFAGC input.41COMPOOUser comparator output.42COMPPIUser comparator for ADIP amplifier feedback circuit.44OPOOUser operational amplifier output.45OPNIUser operational amplifier inverted input.46RFOORF amplifier output. Eye pattern checkpoint.47MORFIIInput of the groove RF signal with AC coupling.                                                                                                                                                                                                                                                                                                                                                                                                                     | 28      | SE     | 0   | Sled error signal output.                                                 |

| 31ADAGCConnects the ADIPAGC capacitor.32ADFGOADIP2 binary value signal output.33AUXO13 output / temperature signal output. Switched with serial commands.34FEOFocus error signal output.35ABCDOReflection light quantity signal output for the main beam servo detector.36BOTMORF/ABCD bottom hold signal output.37PEAKOPeak hold signal output for the RF/ABCD signals.38RFORF equalizer output.39RFAGC-Connects the RFAGC capacitor.40AGCIIRFAGC input.41COMPOOUser comparator output.42COMPPIUser comparator non-inverted input.43ADDCI/OConnects the capacitor for ADIP amplifier feedback circuit.44OPOOUser operational amplifier output.45OPNIUser operational amplifier inverted input.46RFOORF amplifier output. Eye pattern checkpoint.47MORFIIInput of the groove RF signal with AC coupling.                                                                                                                                                                                                                                                                                                                                                                                                       | 29      | ADFM   | 0   | ADIP FM signal output.                                                    |

| 32ADFGOADIP2 binary value signal output.33AUXO13 output / temperature signal output. Switched with serial commands.34FEOFocus error signal output.35ABCDOReflection light quantity signal output for the main beam servo detector.36BOTMORF/ABCD bottom hold signal output.37PEAKOPeak hold signal output for the RF/ABCD signals.38RFORF equalizer output.39RFAGC-Connects the RFAGC capacitor.40AGCIIRFAGC input.41COMPOOUser comparator output.42COMPPIUser comparator non-inverted input.43ADDCI/OConnects the capacitor for ADIP amplifier feedback circuit.44OPOOUser operational amplifier output.45OPNIUser operational amplifier inverted input.46RFOORF amplifier output. Eye pattern checkpoint.47MORFIIInput of the groove RF signal with AC coupling.                                                                                                                                                                                                                                                                                                                                                                                                                                             | 30      | ADIN   | Ι   | ADIP signal comparator input.                                             |

| 33AUXO13 output / temperature signal output. Switched with serial commands.34FEOFocus error signal output.35ABCDOReflection light quantity signal output for the main beam servo detector.36BOTMORF/ABCD bottom hold signal output.37PEAKOPeak hold signal output for the RF/ABCD signals.38RFORF equalizer output.39RFAGC-Connects the RFAGC capacitor.40AGCIIRFAGC input.41COMPOOUser comparator output.42COMPPIUser comparator non-inverted input.43ADDCI/OConnects the capacitor for ADIP amplifier feedback circuit.44OPOOUser operational amplifier output.45OPNIUser operational amplifier inverted input.46RFOORF amplifier output. Eye pattern checkpoint.47MORFIIInput of the groove RF signal with AC coupling.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 31      | ADAGC  | -   | Connects the ADIPAGC capacitor.                                           |

| 34FEOFocus error signal output.35ABCDOReflection light quantity signal output for the main beam servo detector.36BOTMORF/ABCD bottom hold signal output.37PEAKOPeak hold signal output for the RF/ABCD signals.38RFORF equalizer output.39RFAGC-Connects the RFAGC capacitor.40AGCIIRFAGC input.41COMPOOUser comparator output.42COMPPIUser comparator non-inverted input.43ADDCI/OConnects the capacitor for ADIP amplifier feedback circuit.44OPOOUser operational amplifier output.45OPNIUser operational amplifier inverted input.46RFOORF amplifier output. Eye pattern checkpoint.47MORFIIInput of the groove RF signal with AC coupling.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 32      | ADFG   | 0   | ADIP2 binary value signal output.                                         |

| 35ABCDOReflection light quantity signal output for the main beam servo detector.36BOTMORF/ABCD bottom hold signal output.37PEAKOPeak hold signal output for the RF/ABCD signals.38RFORF equalizer output.39RFAGC-Connects the RFAGC capacitor.40AGCIIRFAGC input.41COMPOOUser comparator output.42COMPPIUser comparator non-inverted input.43ADDCI/OConnects the capacitor for ADIP amplifier feedback circuit.44OPOOUser operational amplifier output.45OPNIUser operational amplifier inverted input.46RFOORF amplifier output. Eye pattern checkpoint.47MORFIIInput of the groove RF signal with AC coupling.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 33      | AUX    | 0   | 13 output / temperature signal output. Switched with serial commands.     |

| 36BOTMORF/ABCD bottom hold signal output.37PEAKOPeak hold signal output for the RF/ABCD signals.38RFORF equalizer output.39RFAGC-Connects the RFAGC capacitor.40AGCIIRFAGC input.41COMPOOUser comparator output.42COMPPIUser comparator non-inverted input.43ADDCI/OConnects the capacitor for ADIP amplifier feedback circuit.44OPOOUser operational amplifier output.45OPNIUser operational amplifier inverted input.46RFOORF amplifier output. Eye pattern checkpoint.47MORFIIInput of the groove RF signal with AC coupling.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 34      | FE     | 0   | Focus error signal output.                                                |

| 37PEAKOPeak hold signal output for the RF/ABCD signals.38RFORF equalizer output.39RFAGC-Connects the RFAGC capacitor.40AGCIIRFAGC input.41COMPOOUser comparator output.42COMPPIUser comparator non-inverted input.43ADDCI/OConnects the capacitor for ADIP amplifier feedback circuit.44OPOOUser operational amplifier output.45OPNIUser operational amplifier inverted input.46RFOORF amplifier output. Eye pattern checkpoint.47MORFIIInput of the groove RF signal with AC coupling.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 35      | ABCD   | 0   | Reflection light quantity signal output for the main beam servo detector. |

| 38RFORF equalizer output.39RFAGC-Connects the RFAGC capacitor.40AGCIIRFAGC input.41COMPOOUser comparator output.42COMPPIUser comparator non-inverted input.43ADDCI/OConnects the capacitor for ADIP amplifier feedback circuit.44OPOOUser operational amplifier output.45OPNIUser operational amplifier inverted input.46RFOORF amplifier output. Eye pattern checkpoint.47MORFIIInput of the groove RF signal with AC coupling.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 36      | BOTM   | 0   | RF/ABCD bottom hold signal output.                                        |

| 39RFAGC-Connects the RFAGC capacitor.40AGCIIRFAGC input.41COMPOOUser comparator output.42COMPPIUser comparator non-inverted input.43ADDCI/OConnects the capacitor for ADIP amplifier feedback circuit.44OPOOUser operational amplifier output.45OPNIUser operational amplifier inverted input.46RFOORF amplifier output. Eye pattern checkpoint.47MORFIIInput of the groove RF signal with AC coupling.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 37      | PEAK   | 0   | Peak hold signal output for the RF/ABCD signals.                          |

| 40AGCIIRFAGC input.41COMPOOUser comparator output.42COMPPIUser comparator non-inverted input.43ADDCI/OConnects the capacitor for ADIP amplifier feedback circuit.44OPOOUser operational amplifier output.45OPNIUser operational amplifier inverted input.46RFOORF amplifier output. Eye pattern checkpoint.47MORFIIInput of the groove RF signal with AC coupling.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 38      | RF     | 0   | RF equalizer output.                                                      |

| 41COMPOOUser comparator output.42COMPPIUser comparator non-inverted input.43ADDCI/OConnects the capacitor for ADIP amplifier feedback circuit.44OPOOUser operational amplifier output.45OPNIUser operational amplifier inverted input.46RFOORF amplifier output. Eye pattern checkpoint.47MORFIIInput of the groove RF signal with AC coupling.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 39      | RFAGC  | -   | Connects the RFAGC capacitor.                                             |

| 42COMPPIUser comparator non-inverted input.43ADDCI/OConnects the capacitor for ADIP amplifier feedback circuit.44OPOOUser operational amplifier output.45OPNIUser operational amplifier inverted input.46RFOORF amplifier output. Eye pattern checkpoint.47MORFIIInput of the groove RF signal with AC coupling.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 40      | AGCI   | Ι   | RFAGC input.                                                              |

| 43ADDCI/OConnects the capacitor for ADIP amplifier feedback circuit.44OPOOUser operational amplifier output.45OPNIUser operational amplifier inverted input.46RFOORF amplifier output. Eye pattern checkpoint.47MORFIIInput of the groove RF signal with AC coupling.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 41      | COMPO  | 0   | User comparator output.                                                   |

| 44OPOOUser operational amplifier output.45OPNIUser operational amplifier inverted input.46RFOORF amplifier output. Eye pattern checkpoint.47MORFIIInput of the groove RF signal with AC coupling.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 42      | COMPP  | Ι   | User comparator non-inverted input.                                       |

| 45OPNIUser operational amplifier inverted input.46RFOORF amplifier output. Eye pattern checkpoint.47MORFIIInput of the groove RF signal with AC coupling.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 43      | ADDC   | I/O | Connects the capacitor for ADIP amplifier feedback circuit.               |